Typically, a D flip-flop can only be triggered by either the leading edge or the trailing edge of the clock signal. In some scenario, a flip-flop can be triggered by both edges is required. In this article, an implementation of such flip-flop consists only 2 7400 ICs is proposed.

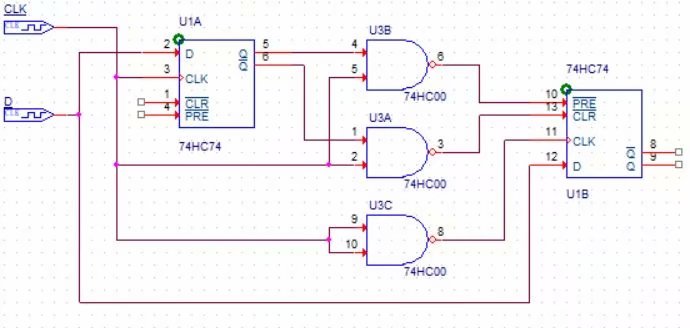

The idea is to use 2 D flip-flops in which one is triggered by the leading edge and the other is triggered by the inverted clock signal. The outputs of these two flip-flops are multiplexed according to the clock signal. The trick in this design is the multiplexing is done with the set and clear functions of the flip-flop, and all logic can thereby be realized with a 74HC74 and a 74HC00:

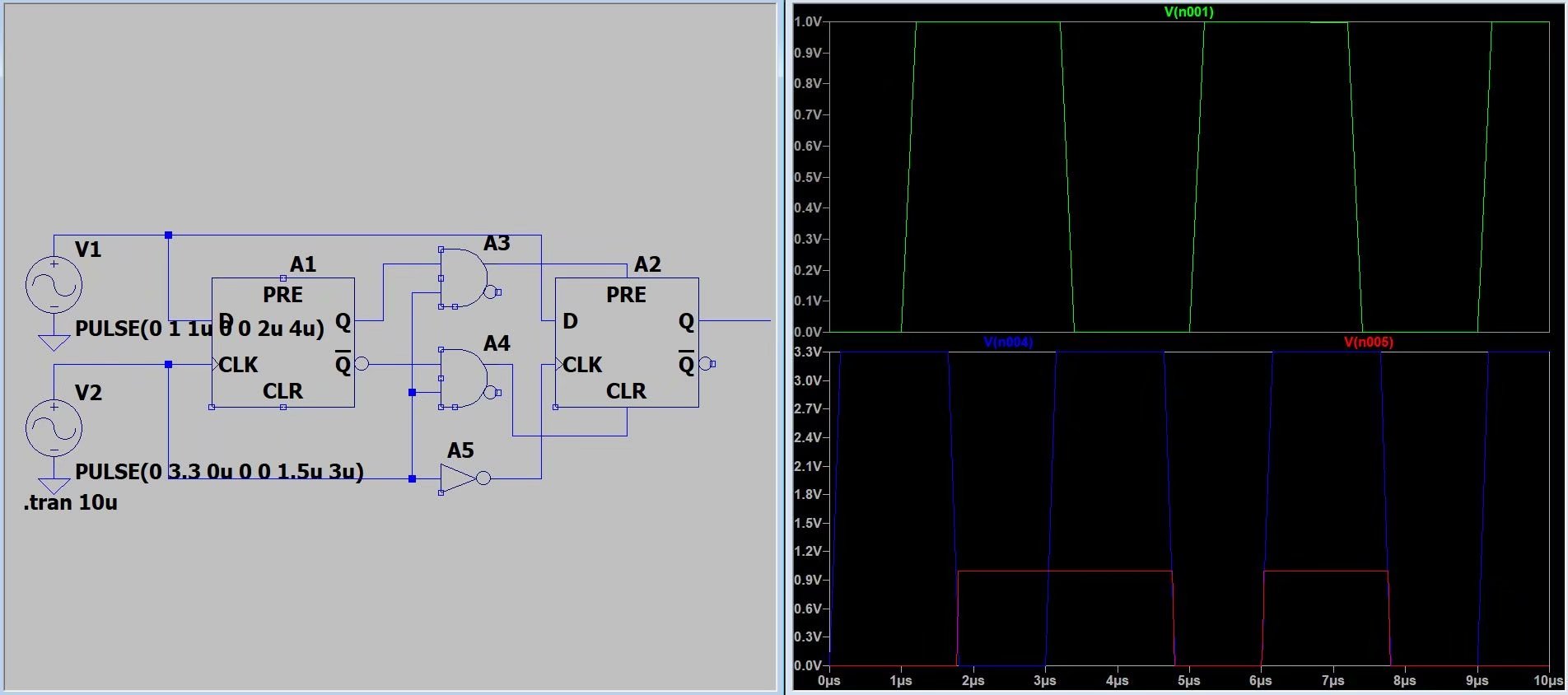

The waveform generated by simulation in LTspice:

green=>D;blue=>CLK;red=>Q

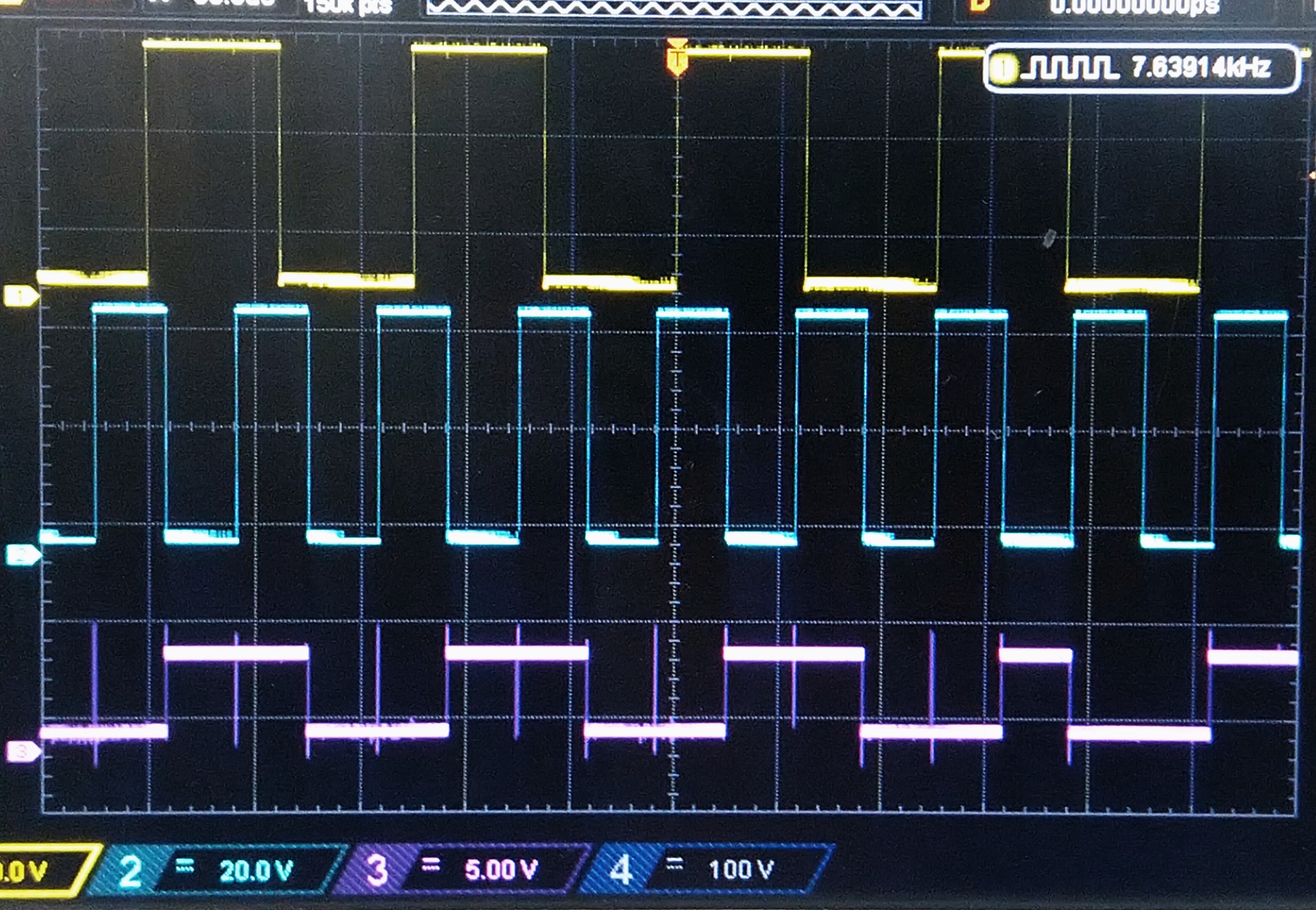

The tested waveform of real circuit: